# Control integrated Power System (CIPOS™)

IKCS12F60AA - Technical Description

AN-CIPOS-1

Authors: Wolfgang Frank

http://www.infineon.com/cipos

Power Management & Drives

| Revision History: | 2008-03 | V1.1 |

|-------------------|---------|------|

| Previous Version: |         |      |

| Page | Subjects (major changes since last revision) |  |

|------|----------------------------------------------|--|

|      | extended section of bootstrapping            |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our web page at <a href="http://www.infineon.com">http://www.infineon.com</a>.

TRENCHSTOP®, CIPOS<sup>TM</sup>, COOLMOS® and COOLSET® are a trademarks of Infineon Technologies AG.

**Edition 2008-03**

Published by Infineon Technologies AG 81726 München, Germany © 2007 Infineon Technologies AG All Rights Reserved.

#### **LEGAL DISCLAIMER**

THE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| 1                                             | Short Description                                                                                                                                                                                                         |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                        | Package Technology       5         Thermal Capabilities and DC Current Rating       5         Mold Compound Characteristic and Creepage Distance at Pins       6                                                          |

| <b>3</b><br>3.1<br>3.1.1<br>3.2               | IGBT and Diode Technology7IGBT7Short Circuit Capability7Diode8                                                                                                                                                            |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Control SectionInput signals (LIN, HIN)9Deadtime turn-off and turn-on10Bootstrapping11Overcurrent Protection (ITRIP)13Supply Voltage (VCC) and Undervoltage Lockout (UVLO)14Thermal Protection15HF Bypassing of DC-link16 |

| 5                                             | Summary of Used Nomenclature                                                                                                                                                                                              |

| 6                                             | <b>References</b>                                                                                                                                                                                                         |

### 1 Short Description

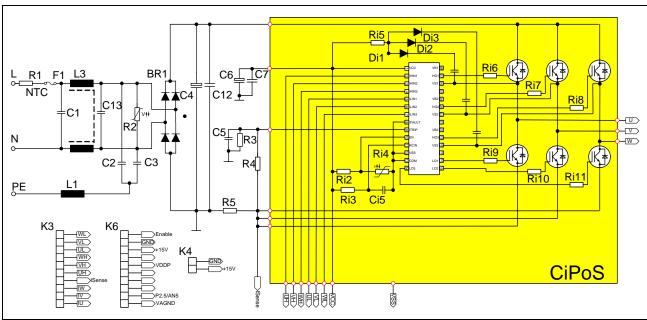

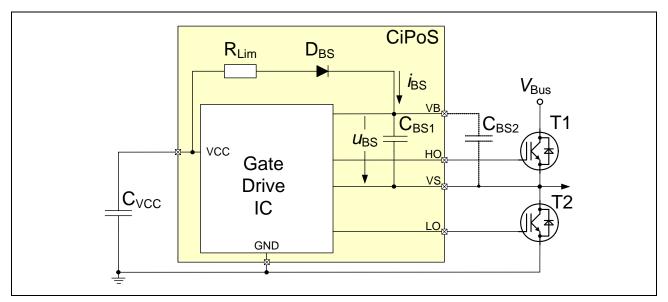

The Control integrated Power System (CIPOS<sup>TM</sup>) is a molded module, which contains all necessary power and gate drive components for setting up a speed variable electric drive according to **Figure 1**. This application note describes particularly the devices IKCS12F60AA and IKCS12F60AB. CIPOS<sup>TM</sup> is a ready to use solution for all drive systems up to a power rating of  $P_{\text{out}} = 1 \text{ kW}$  and is designed for application in consumer drives such as washing machines and air conditioners. Many of the design hints are also valid for other devices.

Please refer to the application note "AN-Gatedrive-6ED003-1" for further information concerning the gate drive IC.

Figure 1 Typical Application of CIPOS<sup>™</sup>

Application Note 4 V1.1, 2008-03

### 2 Package Technology

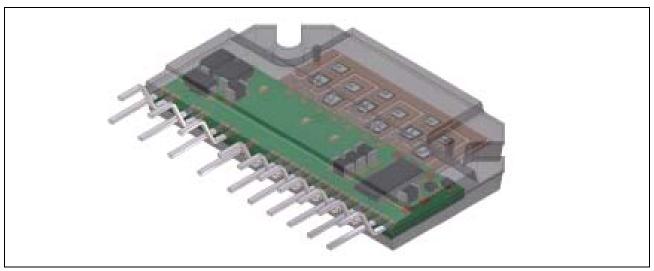

Figure 2 shows a transparent picture of the CIPOS<sup>™</sup> package. Inside the package there is a DCB substrate. It contains all the power components such as the diodes and the IGBT and isolates them from each other and from the heatsink. It is important to note, that this material provides also very low thermal resistance as it is explained more detailed in Section 2.1.

Figure 2 Insight view into the CIPOS<sup>™</sup> package

All the low power components such as the gate drive IC, the gate resistors or the bootstrap circuit are assembled on a PCB. PCB technology allow a very easy routing with EDA tools as they are commonly available.

The mold process is considered for having a solid contact to the PCB and the DCB, so that the only measure in terms of blocking voltage is the voltage withstand capability of the mold compound itself. No further creepage distances are important inside the package, so that routing rules and component placement rules must not be considered. Please refer to **Section 2.2** for the creepage distances and related topics.

### 2.1 Thermal Capabilities and DC Current Rating

The advantage of this material is its low thermal resistance, so that thermal resistances junctio to case of  $R_{\rm thJCl}$  =3.0 K/W f or the IGBT and  $R_{\rm thJCD}$  =4.1K/W for the diode are possible.

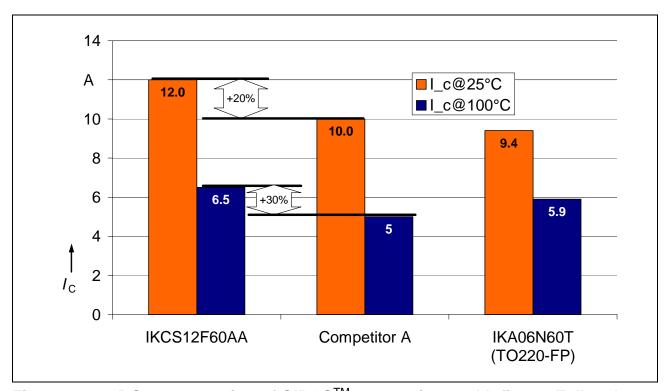

This leads to a significantly lower cost per rated kW. Compared to competitor solutions with similar modules or discrete isolated packages (TO220-fullpack) the DC current rating is higher according to **Figure 3**. The diagram shows the DC rating of the IGBT at a case temperature of  $T_{\rm C} = 25\,^{\circ}{\rm C}$  and  $T_{\rm C} = 100\,^{\circ}{\rm C}$ . Nevertheless, junction is operated at 150°C for CIPOS<sup>TM</sup>. The competitor part is also rated up to 150°C, which is the limit also in this comparison. The DC-current of CIPOS<sup>TM</sup> is higher than the closest competitor by 20% at 25 °C and even 30% at 100°C for the IGBT. The DC current depends on the

Application Note 5 V1.1, 2008-03

output characteristic of the assCIPOSembled IGBT and its thermal resistance  $R_{\text{thJCI}}$ . So both a very good electrical and thermal performance are important to achieve such high values for CIPOS<sup>TM</sup>.

The second solution is a discrete solution which bases on Infineon IKA06N60T. This is a component in TO220 fullpack. It is easy to see, that these devices provide a similar DC rating than the closest competitor. However, this discrete solution is not considered further on in this application note.

Figure 3 DC current rating of CIPOS<sup>TM</sup>, competitor and Infineon Fullpack solution

### 2.2 Mold Compound Characteristic and Creepage Distance at Pins

The performance of the mold compound is essential for calculating the required creepage distances between the pins. The effective parameter is the socalled comparable tracking index (CTI). On basis of the CTI, one can look up and calculate the creepage distance for a given application according to the standards, such as IEC 60664 [1] or IEC 60335 [2] and others including their amendments. The mold compound of CIPOS<sup>TM</sup> has a CTI > 600. Common discrete devices usually have a CTI of approximately 300 to 400, which the applicable working voltage. This is a further advantage of CIPOS<sup>TM</sup>. CIPOSCIPOS<sup>TM</sup> provides a creepage distance of minimum 2.88 mm. This is sufficient for home appliances such as washing machine, vacuum cleaner or air conditioner which are energized from directly from the mains up to 230 V +/- 15%. The creepage distance is even capable of system having a active harmonic filter, e.g. a active boost PFC, which boosts up the working voltage to approximately 400 V.

Application Note 6 V1.1, 2008-03

### 3 IGBT and Diode Technology

#### 3.1 **IGBT**

The assembled IGBT-chips in the IKCS12F60AA are identical to IKP06N60T [3]. They refer to Infineon's TRENCHSTOP® technology. This is the latest non-punch-through (NPT) technology and is particularly developed for consumer drive applications. The IGBT assembled in the CIPOS<sup>TM</sup> module are rated for a maximum junction temperature of  $T_{\perp}$  = 150°C. Please refer to [4] for further information.

#### 3.1.1 Short Circuit Capability

The occurrance of short circuit generates immediately a large amount of heat, which is almost entirely dissipated in the silicon chip.

The 600V TRENCHSTOP® IGBT is specified with a short-circuit robustness up to  $t_{\rm SC}$  = 5 µs at  $T_{\rm J}$  = 150°C,  $V_{\rm GE}$  = 15 V and  $V_{\rm CC}$  = 400 V. Please note here, that the reduction of the short circuit withstand time to 5 µs is not an indicator of reduced short circuit robustness of the TRENCHSTOP® technology. Instead it is a well chosen operational point on a trade-off curve between device performance (i.e. losses under operation conditions) and short circuit withstand time.

In order to understand short circuit capability properly, the known destruction mechanisms shall be discussed. There are principally three mechanisms of short circuit destruction known:

- a) destruction during turn-off due to a latch-up which is related to the device overtemperature,

- b) destruction during the current pulse (current destruction mode) which is not related to the device temperature. Up to now this destruction mode is not fully understood but design measures are known to avoid this kind of destruction mode,

- c) destruction after a successful turn-off (energy destruction) due to thermal run-away of the device as a consequence of the dissipated energy within the pulse. This destruction mode obviously largely depends on the device temperature prior to the short circuit.

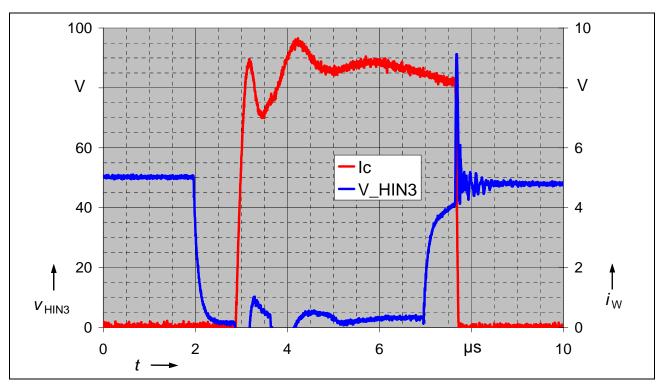

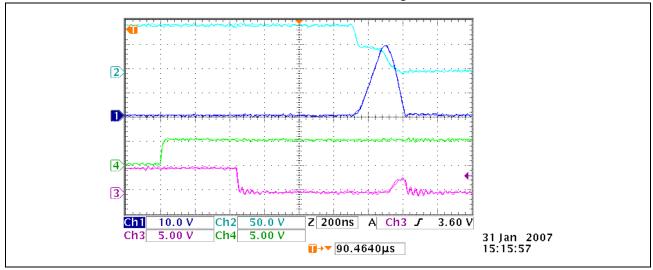

With 600 V TRENCHSTOP®-IGBT exclusively the destruction mode c) can be observed, demonstrating the robust and latch-up free device design. **Figure 4** shows a non-destructive short circuit pulse of IKCS22F60AA at a supply voltage of  $V_{\rm CC}$  = 15 V. Note that the waveforms show conditions well above the specified short circuit capability.

The above discussion clarifies that once the IGBT technology is short circuit robust the further adjustment of a short circuit withstand time is a matter of definition. State-of-theart short circuit detection methods are fast enough to recognize and turn off a short circuit within 5 µs. Therefore the specified short circuit withstand time has been set to 5µs in order to provide products with the best price-performance ratio achieving the biggest advantage for the user.

Application Note 7 V1.1, 2008-03

Figure 4 Short Circuit of IKCS22F60T ( $t_{SC} = 5\mu s$ ,  $V_{CC} = 15 \text{ V}$ ,  $T_{J} = 100 \text{ °C}$ )

#### 3.2 Diode

The diode technology is optimised in order to support the IGBT in best way in a range of the switching frequency from 5kHz to 16 kHz. This is shown in [5]. Particularly in the upper portion of the switching frequency range, the combination of the used EmContechnology and TRENCHSTOP®-technology provides much lower overall losses.

Application Note 8 V1.1, 2008-03

#### 4 Control Section

### 4.1 Input signals (LIN, HIN)

The input signals can be either TTL- or CMOS-compatible. The logic levels can go down to 3.3V. The maximum input voltage of the pins is internally clamped to 10.5 V. However, the recommended voltage range of input voltage is up to 5V. The control pins LIN and HIN are active low.

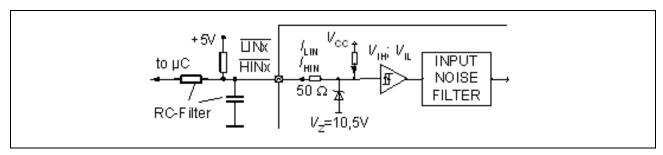

They all have an internal pull-up structure with a pull-up resistor value of nominal 70 k $\Omega$ . The resistor is not subject of the device test and may vary. The integrated pull-up resistors are designed to pull up the internal structures, so that the IC controls a safe state of CIPOS<sup>TM</sup>. An external pull-up circuit is therefore probably necessary. Nevertheless, it is necessary to check, if the connected devices such as microcontrollers are not causing a turn-on signal during exceptions such as reset. The Infineon controller XC866 I/O-pins are configured as inputs during reset and therefore the CIPOS<sup>TM</sup> is able to pull up the  $\mu$ C pins. Harsh environments in terms of EMI may need a C-filter close to the input pins according to Figure 5.

Figure 5 C-filter of input signals and pull-up circuit

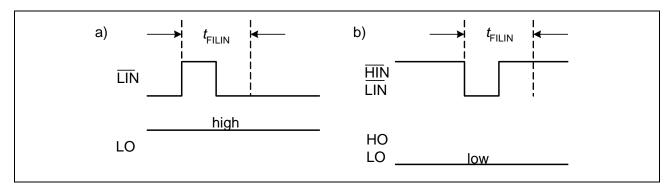

The input noise filter suppresses short pulses and prevents the driven IGBT from excessive switching losses. The input noise filter time at LIN for turning on and off the IGBT and at HIN for turning on the IGBT is typically  $t_{\rm FILIN}$  =270 ns. This means, that an input signal must stay on its level for this period of time in order that the state change is processed correctly according to **Figure 6** and **Figure 7** repectively.

Figure 6 Timing Diagram for Input Filter Characteristic

Application Note 9 V1.1, 2008-03

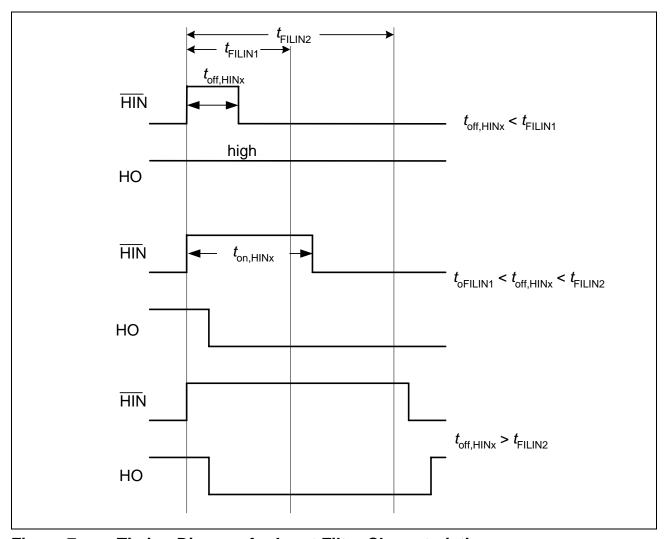

The turn-off of the highside IGBT is processed, when a HIGH-level signal at the pins /HIN occurs for longer than typically  $t_{\rm FILIN1}$  =200 ns the according to b) of **Figure 7**. Otherwise the change in the status of the input signal /HIN will be skipped.

Figure 7 Timing Diagram for Input Filter Characteristic

A full pulse is transmitted , if it is longer than  $t_{\rm HIN}$  = 350 ns typically. However, it is recommended to stay above a minimal pulse duration of 1  $\mu$ s. This means, that also an external RC-filter is not necessary in most cases.

#### 4.2 Deadtime turn-off and turn-on

It is mandatory to establish a deadtime between the turn-off of a high side transistor and the following turn-on of a low side transistor. The driver IC inside the CIPOS<sup>TM</sup> package is generating such a deadtime of typically DT = 325ns. This is a feature, which helps to prevent short circuit due to overlapping of gate voltage at the gate pins of the IGBT.

However, the ingrated IGBT have specific delay times for turn-on and turn-off. They are not symmetric. The turn-off delay time for IKCS12F60AA is typically  $t_{d(off)} = 400$  ns,

Application Note 10 V1.1, 2008-03

whereas the turn-on delay time is typically  $t_{d(on)} = 20$  ns. The fall and rise times of the IGBT have to be considered as well. The fall time for IKCS12F60AA is typically  $t_{\rm f} = 70$  ns and the rise time is typically  $t_{\rm f} = 20$  ns.

The resulting time of the IGBT for turning it totally off is therefore  $t_{\rm d(off)} + t_{\rm f} = 400~{\rm ns} + 70~{\rm ns} = 470~{\rm ns}$ . The corresponding delay for turning it on is  $t_{\rm d(on)} + t_{\rm f} = 20~{\rm ns} + 20~{\rm ns} = 40~{\rm ns}$ . The difference of both is  $\Delta t = 470~{\rm ns} - 40~{\rm ns} = 430~{\rm ns}$ , which is larger than the deadtime of the driver IC (DT = 325 ns). The generated deadtime by the driver IC is therefore not sufficient to avoid a short circuit at all conditions. The mentioned intervals  $t_{\rm d(off)}$ ,  $t_{\rm d(on)}$ ,  $t_{\rm f}$  and  $t_{\rm f}$  are generally increasing for IGBT with higher current ratings. Therefore the difference  $\Delta t$  is also larger for IKCS22F60AA. Figure 8 shows the input signals (red and green) as well as the corresponding phase output voltage (light blue) and the phase output current (dark blue) for IKCS22F60AA. It can be seen that a deadtime of approx. 440 ns is not sufficient in order to avoid a shoot through for about 250 ns.

Figure 8 Bad Timing of Input Signals

This means, that the deadtime must be set by the microcontroller. A minimum deadtime of 1  $\mu$ s for IKCS12F60xx is recommended in order to avoid short term short circuit of a half bridge leg.

### 4.3 Bootstrapping

Bootstrapping is a common method of pumping charges from a low potential to a higher one. With this technique a supply voltage for the floating highside sections of the gate drive can be easily established according to **Figure 9**. It is only the effective circuit shown for one of the three half bridges. The current limiting resistor RLim is connected to each of the three bootstrap diodes in the module. Please refer to the datasheet in order to see the internal schematic.

The first puls of transistor T2 will force the potential of pin VS to GND. The resulting dv/dt leads to a displacement current  $i_{BS}$  into the capacitor  $C_{BS1}$ . The current  $i_{BS}$  is a pulse current and therefore the ESR of the capacitor  $C_{BS1}$  must be very small in order to avoid

Application Note 11 V1.1, 2008-03

losses in the capacitor, that result in lower lifetime of the capacitor. The CIPOS<sup>TM</sup> provides the pin VB, so that additional external capacitors can be used according to  $C_{BS2}$  in **Figure 9**. The integrated capacitor is  $C_{BS1} = 100$ nF.

Figure 9 Bootstrap circuit for the supply of a highside gate drive

This pin is on high potential again after transistor T2 is turned off. But now the bootstrap diode  $D_{BS}$  blocks a reverse current, so that the charges on the capacitor remain the same. The bootstrap diode also takes over the blocking voltage between pin VB and VCC. The voltage of the bootstrap capacitor can now supply the highside gate drive sections. The voltage of bootstrap capacitor is approximately

$$V_{\rm BS} \approx V_{\rm CC} - V_{\rm FBS} \tag{1}$$

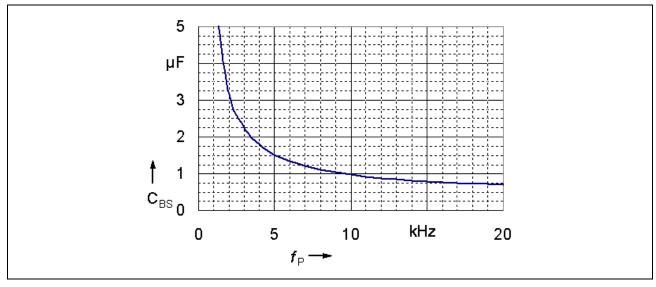

A current limiting resistor  $R_{Lim}$  reduces the peak of the pulse current during the turn-on of transistor T2. The pulse current will occur at each turn-on of transistor T2, so that with increasing switching frequency the capacitor  $C_{BS1}$  and  $C_{BS2}$  are charged more frequently. Therefore a smaller capacitor is suitable at higher switching frequencies. A low leakage current of the highside section is very important in order to keep the bootstrap capacitors small. The bootstrap capacitor is discharged by two effects: The leakage current and the gate charge of the transistor to be turned on. The calculation of the bootstrap capacitor results in

$$C_{BS} = \frac{i_{QBS1} \cdot t_P + Q_G}{\Delta V_{RS}}$$

(2)

with  $i_{QBS1}$  being the quiescent current of the highside section,  $t_P$  the switching period,  $Q_G$  the total gate charge and  $\Delta v_{BS}$  the voltage drop at the bootstrap capacitor within a switching period. Please note here, that **Equation (2)** is valid for continous switching according to the switching frequency. The use of space vector modulations can cause

Application Note 12 V1.1, 2008-03

periods up to 60° (electrical), in which no switching of the low side transistor of a half bridge occurs. This effects the bootstrap capacitor size, especially for low output current (motor current) frequencies. In this case the variable  $t_{\rm P}$  must be set to the longest period of no switching. **Figure 10** shows the curve corresponding to **Equation (2)** for a continuous sinusoidal modulation, if the voltage ripple  $\Delta v_{\rm BS} = 0.1$ V. The recommended bootstrap capacitance is therefore in the range up to 4.7µF for most switching frequencies.

Figure 10 Recommended size of the bootstrap capacitor as a function of the switching frequency  $f_P$  at a supply voltage of  $V_{DD} = 15V$

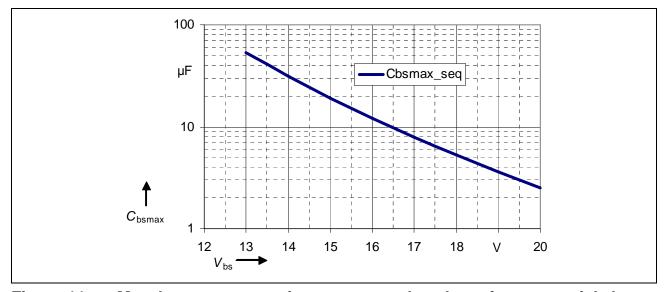

Please note, that one of the limiting factors of the bootstrap capacitor design is the power capabilities of the bootstrap resistor. There are different ways to reduce the stress of the resistor, such as loading the capacitance phase by phase sequentially with a period of approximately 50ms between each phase being charged. **Figure 11** shows the max. bootstrap capacitance for sequentially charging the bootstrap capacitances.

Figure 11 Max. bootstrap capacitance vs. supply voltage for sequential charge

Application Note 13 V1.1, 2008-03

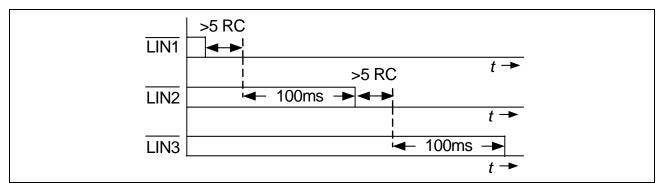

It is necessary for the sequential charging of the bootstrap capacitors, that the turn-on period of the low side transistors is a multiple of the charging RC time constant. It should be larger than 5\*RC in order to ensure, that the capacitors are properly charged.

Figure 12 Possible charging scheme for bootstrap capacitors

### 4.4 Overcurrent Protection (ITRIP)

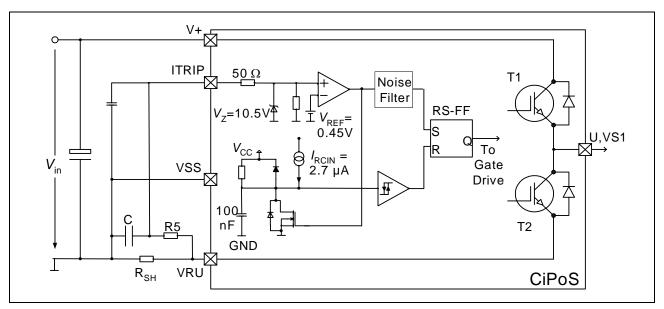

The overcurrent protection is a major feature of IKCS12F60AA. It is realised by accessing the shunt signal  $R_{SH}$  according to **Figure 14**. The CIPOS<sup>TM</sup> stops operation as soon as the voltage level at pin ITRIP is higher than typically  $V_{IT,TH+} = 0.45$  V. This corresponds to a current level of

$$I_{ITRIP} = \frac{V_{IT, TH+}}{R_{SH}}$$

(3)

An internal comparator is triggered and sets a latch flip-flop. This flip-flop inhibits the output sections of both highside and lowside transistors. After triggering the ITRIP-comparator, a current source charges a RC-network. The CIPOS<sup>TM</sup> restarts operation after approximately 5ms.

The very low threshold of the ITRIP comparator allows to feed the shunt signal directly into the ITRIP pin. As a result, the voltage divider is not necessary. A RC-filter, which attenuates voltage spikes in the shunt signal, is recommended here instead.

A voltage divider is not necessary here, because the trigger level of 0.45 V is low enough, in order to directly connect the output of the RC-filter with pin ITRIP.

Application Note 14 V1.1, 2008-03

Figure 13 Structure of the overcurrent protection and overcurrent recovery

The ITRIP pin is internally clamped by internal zener diode to 10.5 V.

#### 4.5 Supply Voltage (VCC) and Undervoltage Lockout (UVLO)

The supply voltage covers a range up to maximum 20 V. Above this value an internal clamp circuit will limit this parameter to 20 V. It is necessary to assure by design, that the voltage does not increase further than 20 V, because the activation of the internal clamp causes local losses, which can lead to a destruction of the device. Temporarily higher voltages can occur, if the auxiliary (AUX-) power supply is not operating properly or if the supply voltage of CIPOS<sup>TM</sup> is not directly controlled by the AUX-supply. The recommended operating range is up to 17.5V, because there is still a good margin the clamp limit.

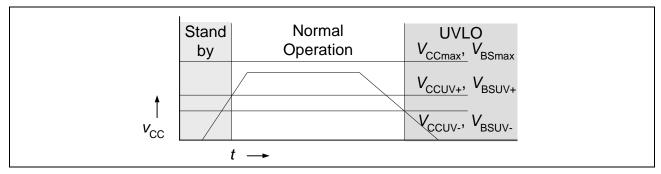

CIPOS<sup>TM</sup> will move from standby operation into normal operation, when the supply voltage at pin VCC is higher than 12 V typically according to **Figure 14**. The beginning of the pulse operation will pump charges into the bootstrap capacitor, so that the bootstrap voltage will rise accordingly. As soon as the bootstrap voltage is higher than 12 V also the highside sections of CIPOS<sup>TM</sup> are clear for operation.

The CIPOS<sup>TM</sup> operates in normal mode down to a supply voltage of 10.3 V for both the bootstrap voltage and the lowside supply voltage. This is important in order to prevent the IGBT from too low gate voltage, which could damage the IGBT due to excessive losses.

Application Note 15 V1.1, 2008-03

Figure 14 Voltage levels for start up and UVLO

#### 4.6 Thermal Protection

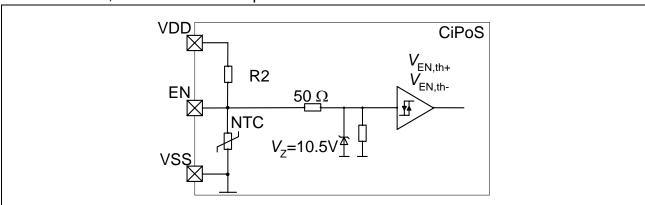

The thermal protection is realised with a NTC-resistor according to **Figure 15**. The protection is entirely inside CIPOS<sup>TM</sup> and the tap of the voltage divider will trigger the comparator, when the voltage reaches  $V_{\rm EN,th}$  = 1.32 V typ. This point represents a temperature at the location of the NTC of 125°C, which is also the maximum operating temperature of the gate drive IC. The NTC is located on the PCB of CIPOS<sup>TM</sup>.

The positive going threshold of the comparator is  $V_{\text{EN,th+}} = 2.1 \text{ V}$  typically, which represents a temperature of approximately 110°C. This means that the CIPOS<sup>TM</sup> must cool down first, before it restarts operation.

Figure 15 Thermal Protection with NTC

It is important for CIPOS<sup>TM</sup> to protect the gate drive IC from overtemperature. However, the thermal protection should also protect the power semiconductors from overheating. It is therefore necessary to have a good thermal coupling of the semiconductors to the NTC. A sufficient way of coupling the DCB and the PCB is to choose a heatsink, which covers the complete backside of CIPOS<sup>TM</sup>. This leads to a good heat transfer via the heatsink itself. The reaction time of the NTC is then approximately 150 seconds.

The NTC circuit according to **Figure 15** is dependent on the supply voltage of CIPOS<sup>TM</sup>, because the voltage at the tap varies at a constant temperature, if the supply voltage changes. This means, that also the trigger temperature of the overtemperature protection

Application Note 16 V1.1, 2008-03

can vary, if the supply voltage is not constant. The NTC has a typical resistance at 25°C of 100 k $\Omega$  and a socalled B-constant of 4250. The resistance of the NTC is therefore

$$R_{NTC}(T) = R_0 e^{B\left(\frac{1}{T} - \frac{1}{T0}\right)}$$

(4)

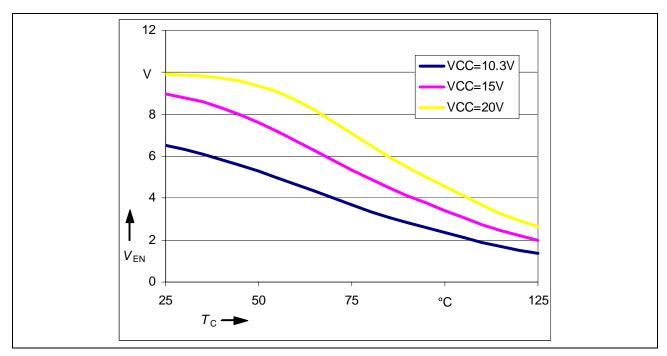

where  $R_0$  =100 kW, B = 4250 K, T0 = 298 K, T is the NTC-temperature in Kelvin. The overall characteristic of the voltage at pin EN is given in **Figure 16**

Figure 16 Typical characteristic of pin EN as a function of temperature

### 4.7 HF Bypassing of DC-link

A bypass capacitor for shorting the high frequency portion of the currents, which occur due to the switch mode operation of the inverter is recommended. The capacitor should be located as close to the pins "V+" and "VSS" as possible. This results in small parasitic inductances in respect of the high-side DC-link track as well as the emitter-side tracks. It also keeps the disturbance in terms of EMI concentrated close to the CIPOS<sup>TM</sup> module.

Application Note 17 V1.1, 2008-03

### **5** Summary of Used Nomenclature

### Physics:

| General identifiers:  Across area  b, Bmagnetic inductance  d, Dduty cycle  ffrequency  i, Icurrent                                                                                                                                                                                                                                                      | Special identifiers: $A_{L}$ inductance factor $V_{(BR)CES}$ collector-emitter breakdown voltage of IGBT $V_{F}$ forward voltage of diodes $V_{rrm}$ maximum reverse voltage of diodes      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Nnumber of turns</li> <li>p, Ppower</li> <li>t, Ttime, time-intervals</li> <li>v, Vvoltage</li> <li>Wenergy</li> <li>ηefficiency</li> </ul>                                                                                                                                                                                                     | big letters: constant values and time intervals small letters: time variant values                                                                                                          |

| Components:  Ccapacitance  Ddiode  ICintegrated circuit                                                                                                                                                                                                                                                                                                  | Lresistor TRtransformer                                                                                                                                                                     |

| Indices:                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                             |

| ACalternating current value DCdirect current value BEbasis-emitter value CCollector value CScurrent sense value EBmitterr value GGate value OPTOoptocoupler value Pprimary side value Pkpeak value Rreflected from secondary to primary side Sreflected from secondary to primary side Ssecondary side value UVLOundervoltage lockout value Zzener value | fmin value at minimum pulse frequency irunning variable ininput value maxmaximum value minminimum value offturn-off value onturn-on value outoutput value ppulsed rippulsed ripripple value |

Application Note 18 V1.1, 2008-03

#### 6 References

- [1] International Electrotechnical Commission: IEC 60664-1 Insulation coordination for equipment within low-voltage systems Part 1: Principles, requirements and tests; International Standard; IEC, Geneva, Switzerland.

- [2] International Electrotechnical Commission: IEC 60335-1 Household and similar electrical appliances Safety Part1: Part 1: General requirements; International Standard; IEC, Geneva, Switzerland.

- [3] .Infineon Technologies: IKP06N60T; Datasheet; Infineon Technologies, Germany, 2006.

- [4] Infineon Technologies: TRENCHSTOP®-IGBT 600 V Next Generation IGBT for Motor Drive Application; Application Note V 1.1; Infineon Technologies, Germany, 2006.

- [5] W. Frank, H. Hüsken: Considerations on Design of antiparallel Diodes for Combination of IGBT and Diodes in one Package; Proceedings of the 26th Conference on Power Control and Intelligent Motion PCIM 2005; Nuremberg, Germany; 2005.

- [6] Infineon Technologies: IPOSIM.xls; Simulation Tool; http://www.eupec.com; Infineon Technologies; Germany; 2005

Application Note 19 V1.1, 2008-03

www.infineon.com

Published by Infineon Technologies AG